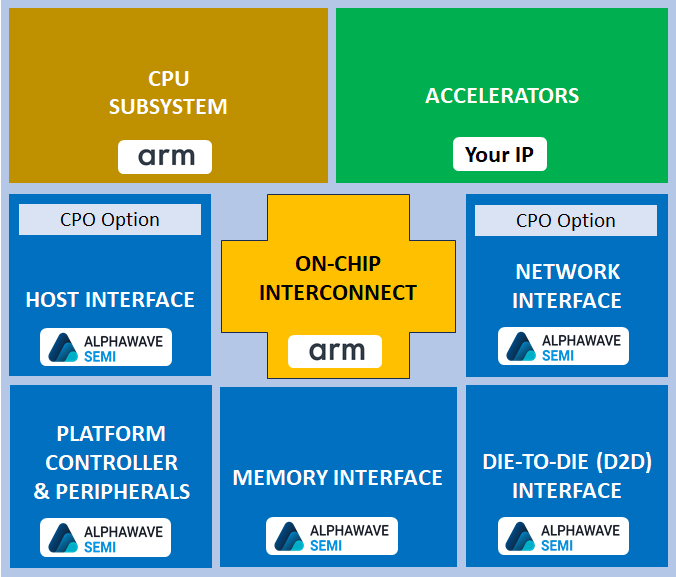

Composable SoC

Alphawave Semi has a broad selection of leading-edge IP controller blocks and interfaces to which you can add your own custom accelerator, interface, or security IP. For CPU subsystems, we have collaborated with Arm as part of the Arm Total Design ecosystem based on Arm Neoverse Compute Subsystems (CSS) for faster development time with lower risk.