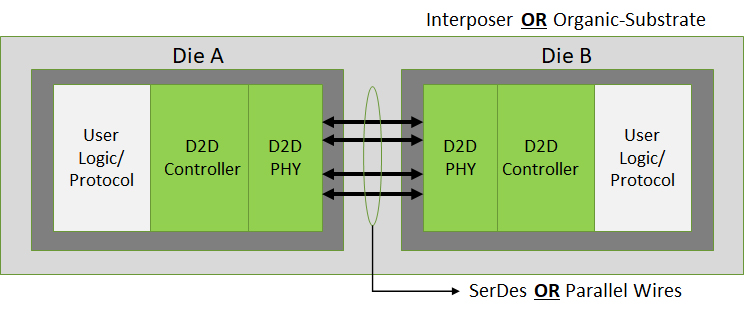

UCIe Die-to-Die (D2D) IP Subsystem

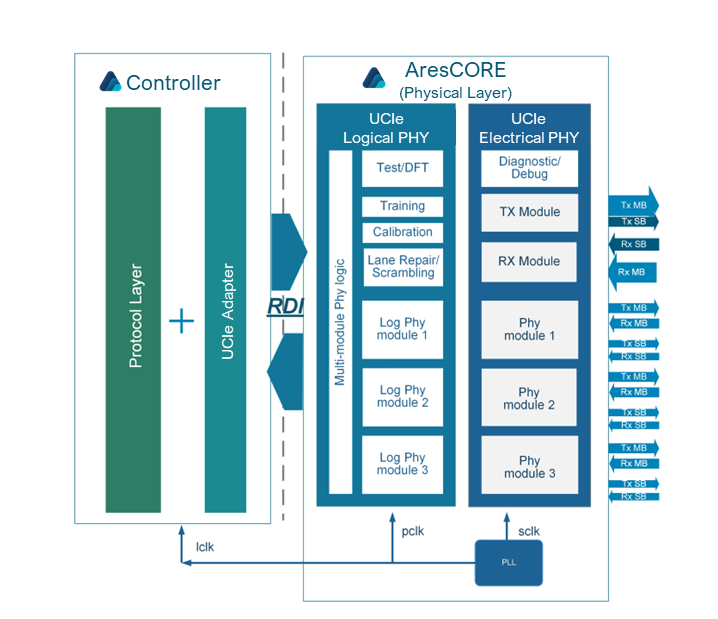

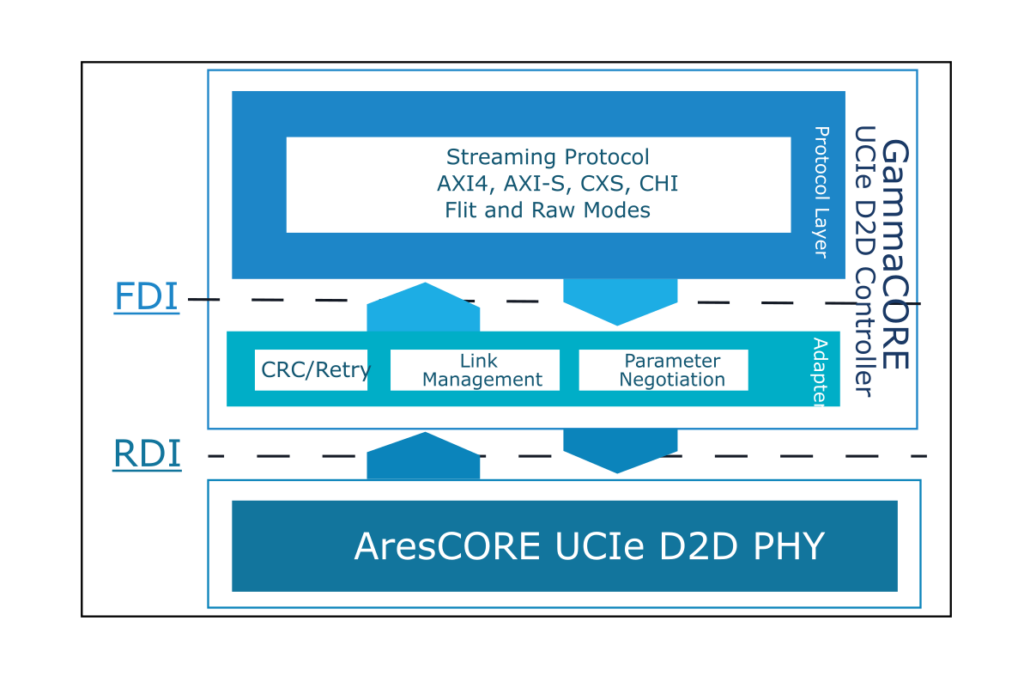

Alphawave’s UCIe Die-to-Die IP Subsystem offers a unique solution with extremely low power, high throughput, and low latency links enabling faster time to integration for heterogenous chiplet connections in wired communications, Artificial Intelligence (AI), High Performance Computing (HPC), Datacenters and Networking applications.