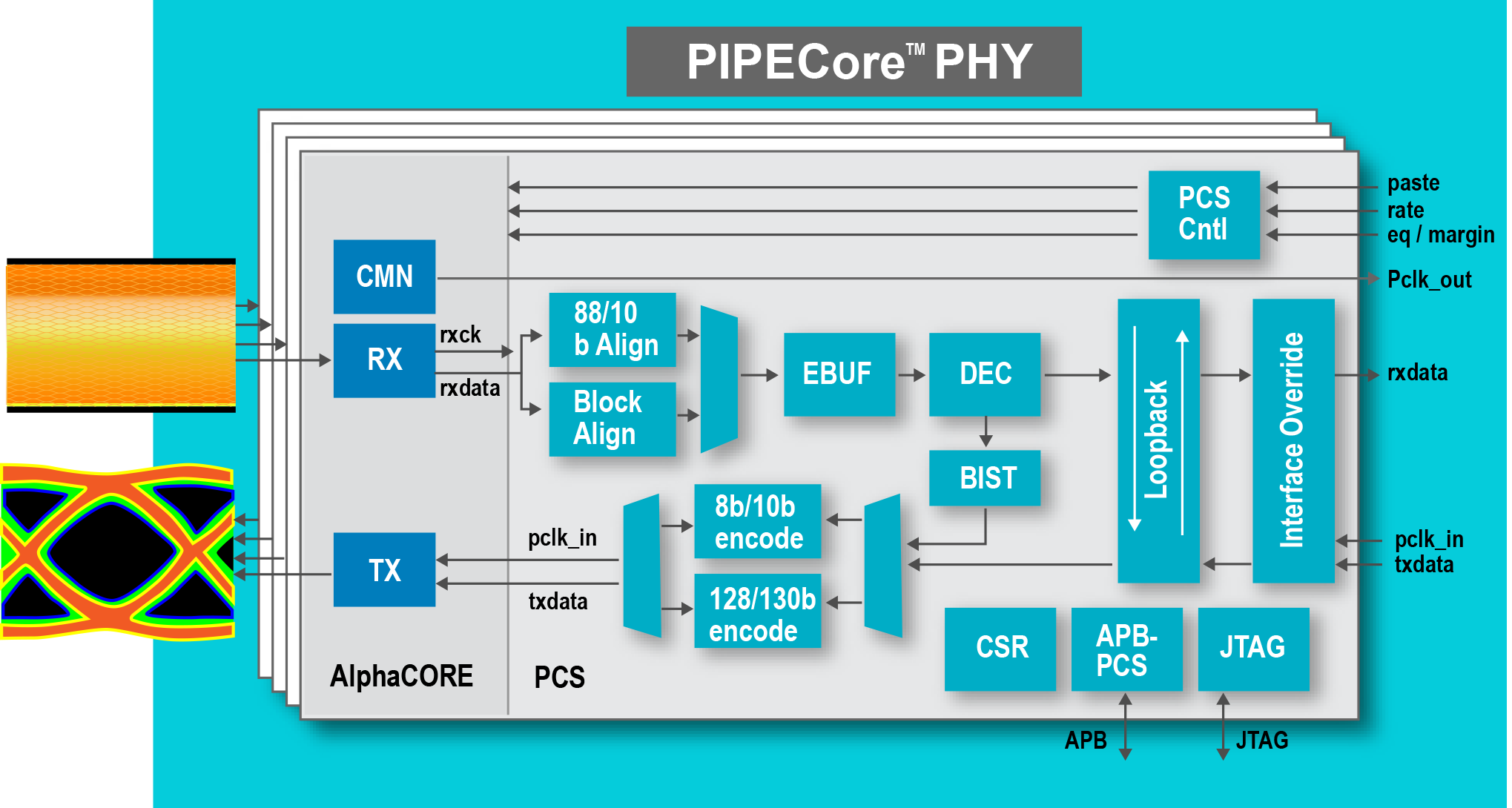

PipeCORE PCI-Express and CXL PHY

1 to 64 Gbps PCI-Express (PCIe) 6.0 and CXL 3.0 PHY

The Alphawave PipeCORE PHY IP is a high-performance, low-power, PCIe 1.0 to PCIe 6.0 PHY, that is capable of also operating at 64 Gbps PAM4 PCI Express 6.0 rates (2.5/5/8/16/32/64 GT/s). It includes a hardened PMA layer and a soft PCS layer deliverable. PipeCORE is based on the industry leading AlphaCORE DSP architecture.