HermesCORE HBM3 Controller

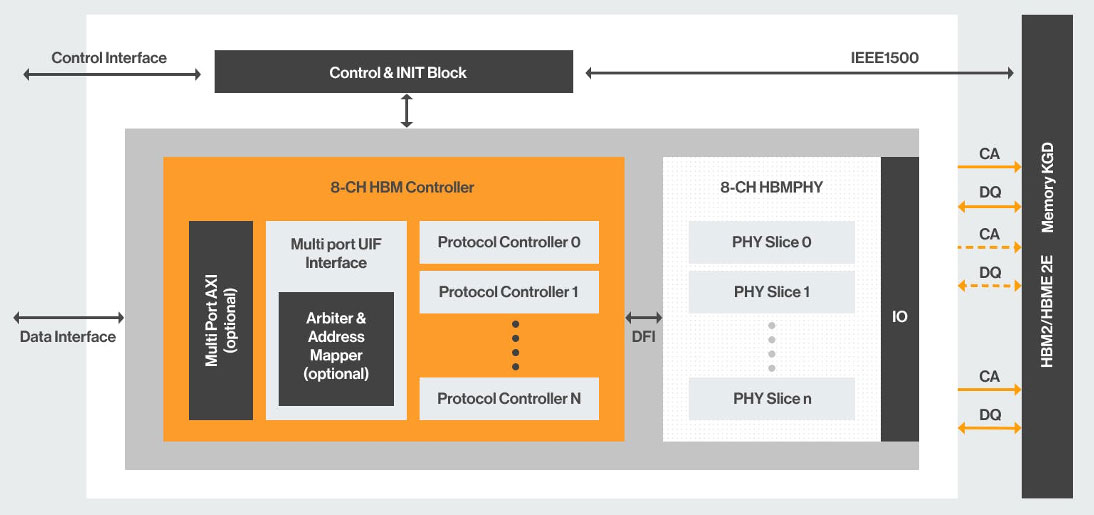

The HermesCORE High-Bandwidth Memory Generation 3 (HBM3) controller is ideal for applications involving graphics, high-performance computing, high-end networking, and communications that require very high memory bandwidth, lower latency, and more density. The controller can be delivered as part of a complete HBM3 memory subsystem with an integrated HBM3 PHY.