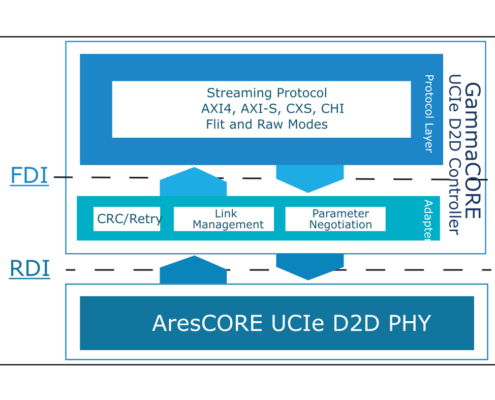

GammaCORE UCIe Die-to-Die Controller IP

GammaCORE is a highly configurable and customizable Universal Chiplet Interconnect Express (UCle™) Die-to-Die Controller IP implementing the latest UCIe 2.0 specification and supporting UCIe Streaming protocol applications.

With Alphawave’s AresCORE D2D PHY IP, GammaCORE provides the complete UCIe solution for an open and robust chiplet ecosystem.