Exploring Alphawave Semi’s AlphaCHIP1600-IO Chiplet and its Real-World Applications

By Shivi Arora, ASIC IP Solutions, and Sue Hung Fung, Product Line Manager

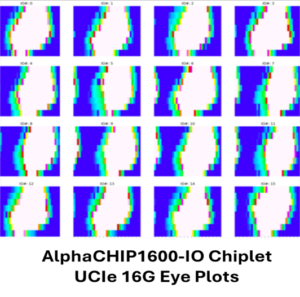

Meet the AlphaCHIP1600-IO: a high-bandwidth, low-latency, and power-efficient chiplet built for next-generation connectivity. It integrates the UCIe™ standard for die-to-die communication alongside support for PCIe® 6.0, CXL® 3.1, and 800G Ethernet protocols—enabling robust compute and networking interfaces. Designed with up to 16 lanes of 112G multi-standard SerDes PHY, this chiplet delivers an impressive total bandwidth of up to 1.6 Tbps.

As AI and ML infrastructures, data centers, networking, telecom, cloud, and edge computing continue to evolve, the demand for modular and scalable system integration is accelerating. The AlphaCHIP1600-IO chiplet has been purpose-built for use in SiPs (System-in-Packages) targeting these next-generation platforms. In these environments, robust connectivity across servers, racks, and storage systems is critical—and chiplets offer the modular upgrade path needed to meet this demand.

For SoC designers working on AI data centers and other high-performance applications, traditional monolithic die designs have hit the reticle limit. To scale compute and bandwidth further, disaggregation is essential. Chiplet-based architectures offer a strategic solution by offloading I/O functionality and interfaces from the main die, enabling smaller die sizes, improved yield, and increased design flexibility.

For SoC designers working on AI data centers and other high-performance applications, traditional monolithic die designs have hit the reticle limit. To scale compute and bandwidth further, disaggregation is essential. Chiplet-based architectures offer a strategic solution by offloading I/O functionality and interfaces from the main die, enabling smaller die sizes, improved yield, and increased design flexibility.

By adopting Alphawave Semi chiplet architectures, design teams can significantly reduce time to market and avoid costly redesigns. This approach also lowers NRE (non-recurring engineering) and manufacturing costs by allowing multiple dies, potentially built on different process nodes, to be integrated on a single package substrate. The AlphaCHIP1600-IO chiplet simplifies this integration by offering high-speed I/O connectivity with support for PCIe®, CXL®, and Ethernet protocols—all through a UCIe™ interface.

This achievement also reflects Alphawave Semi’s deep alignment with industry standards and momentum around chiplet-based design. As Brian Rea, Chair of the UCIe Consortium’s Marketing Working Group, noted, “UCIe™ (Universal Chiplet Interconnect Express™) standardizes the interconnect interface between chiplets, ensuring compatibility and ease of integration across different generations and types of chiplets. We are excited to see Alphawave Semi's commitment to innovation and excellence in advancing the chiplet ecosystem with UCIe technology.”

By integrating UCIe into a silicon-proven I/O chiplet, Alphawave Semi is setting the foundation for scalable and interoperable chiplet solutions that support the growing demands of AI, HPC, and cloud infrastructure.

AlphaCHIP1600-IO Chiplet: Real-World Use Cases for High-Bandwidth Connectivity

End-to-End Ethernet Traffic

Alphawave Semi’s AlphaCHIP1600-IO chiplet demonstrates robust, high-performance Ethernet connectivity by driving a Direct Attach Copper (DAC) link with consistently strong signal integrity and healthy link margins.

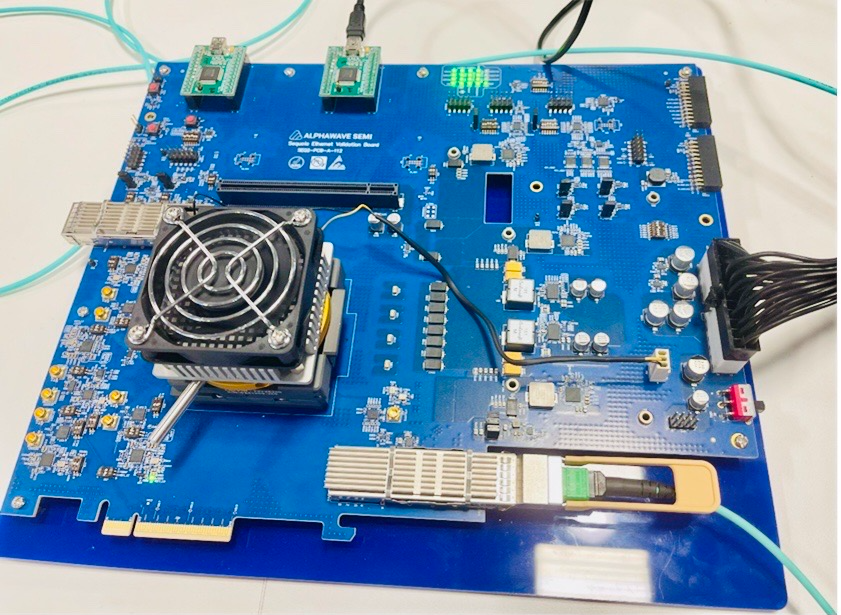

In the demonstration below, Ethernet packets are generated by a NIC connected to a host and transmitted end-to-end across two AlphaCHIP1600-IO chiplets, which are interconnected via the UCIe™ standard.

This setup highlights the chiplet’s ability to deliver scalable and flexible Ethernet connectivity—enabling both scale-up bandwidth and scale-out system expansion—making it ideally suited for next-generation data center and AI workloads.

End-to-End Ethernet over AlphaCHIP1600-IO Chiplets

Demonstration Highlights

- Robust End-to-End Ethernet Connectivity

The AlphaCHIP1600-IO chiplet drives a QSFP-DD DAC link with strong signal integrity and consistently reliable link margins. - UCIe-Based Chiplet Interconnection

This demo showcases Ethernet packet transfer between two AlphaCHIP1600-IO chiplets using the Universal Chiplet Interconnect Express (UCIe) standard. - Scalable and Flexible Architecture for AI and Data Centers

Designed to support both scale-up bandwidth and scale-out system expansion, the architecture is ideal for future-proofing high-performance data center and AI workloads.

Linear Pluggable Optics and Live Interoperability

800G Optical Connectivity: AlphaCHIP1600-IO + Lessengers’ VCSEL LPO

At OFC 2025, in the OIF live interoperability booth, Alphawave Semi successfully demonstrated the AlphaCHIP1600-IO chiplet connected to a QSFP-DD SR8 Linear Pluggable Optics (LPO) VCSEL module. The setup received Ethernet traffic over optical fiber from a switch, achieving reliable link-up and a healthy Bit Error Rate (BER) margin—clearly validating the chiplet’s robust signal integrity and high-performance capabilities.

This live demonstration proved the flexibility and scalability of the AlphaCHIP1600-IO chiplet for data center and cloud-scale networking. Paired with a VCSEL-based LPO, the solution meets the bandwidth and efficiency demands of next-generation scale-up and scale-out architectures while maintaining signal integrity over extended optical links.

Demonstration Highlights

- Chiplet-Driven 800G Optical Connectivity

AlphaCHIP1600-IO chiplet powers Lessengers’ 800G QSFP-DD SR8 Linear Pluggable Optics (LPO) module for advanced high-speed optical data transmission. - Ethernet Link to Switch Infrastructure

Demonstrates reliable high-speed Ethernet connectivity, successfully linking to a switch in a real-world network scenario. - Stable BER Across Long-Distance Optical Links

Delivers consistent, high-performance Bit Error Rate (BER) over VCSEL-based LPO modules, even across fiber links extending up to 100 meters.

PCIe Link up to a Host System

AlphaCHIP1600-IO Chiplet Link-Up to Host Demonstration

The AlphaCHIP1600-IO chiplet has successfully demonstrated a reliable PCIe® link-up to a host system, showcasing its versatility and robust plug-and-play capabilities.

In this demonstration, the AlphaCHIP1600-IO chiplet was configured as an Endpoint device and connected to a host system motherboard acting as the Root Complex. The system achieved a healthy link initialization within a standard PCIe plug-and-play environment—proving the chiplet’s readiness for I/O disaggregation and its applicability across a wide range of compute architectures.

Demonstration Highlights

- AlphaCHIP1600-IO PCIe PHY/Controller Link-Up

The chiplet established a stable and healthy PCIe link with the host system, demonstrating healthy performance signal integrity and interoperability. - Plug-and-Play Simplicity

Designed for modern multi-chiplet ecosystems, the AlphaCHIP1600-IO effortlessly negotiates link-up in PCIe-compliant systems without manual intervention. - Flexible Endpoint/Root Complex/Switch Integration

The chiplet operates as an Endpoint while the host system acts as the Root Complex — a configuration ideal for modular designs where scalability and interoperability are paramount. The chiplet can also be configured as Root Complex or Switch mode.

Conclusion

At Alphawave Semi, our mission is to enable high-performance, scalable connectivity solutions for the next generation of compute and data infrastructure. Whether you're designing for AI/ML clusters, cloud infrastructure, or hyperscale data centers, Alphawave Semi is driving the future of chiplet-based systems with high-speed electrical or optical connectivity.

The silicon demonstrations above highlight Alphawave Semi’s continued innovation in delivering scalable, standards-compliant chiplet solutions. Whether you're architecting next-generation AI, HPC platforms, or disaggregated data center systems, the AlphaCHIP1600-IO chiplet is engineered to meet your performance, flexibility, and interoperability needs.

Validated samples are now available, complete with hardware, firmware, and software support.

Ready to learn more?

Let’s discuss how the AlphaCHIP1600-IO chiplet can accelerate your connectivity roadmap.

Contact Us or Download the Datasheet to get started

In this video from Chiplet Summit, learn about Alphawave Semi’s new AlphaCHIP1600-IO, an industry-first multi-protocol IO chiplet supporting PCIe Gen 6, CXL 3.1, and 800G Ethernet.

Read more about Alphawave Semi’s tape-out of the industry’s first off-the-shelf multi-protocol I/O connectivity chiplet on TSMC’s 7nm process here.

Learn more about how Alphawave Semi drives innovation in hyperscale AI accelerators with I/O chiplet for Rebellios Inc. here.