Q3-2025-Waverider Pulse UCIe Special

Welcome to the Waverider Pulse UCIe Special…

Research: UCIe Interoperability

As chiplet-based designs become essential for future AI systems, ensuring interoperability is a key research area. Intel and Alphawave Semi have partnered to investigate UCIe die-to-die communication through extensive pre-silicon simulations study. Learn about the challenges identified and insights gained from their joint effort.

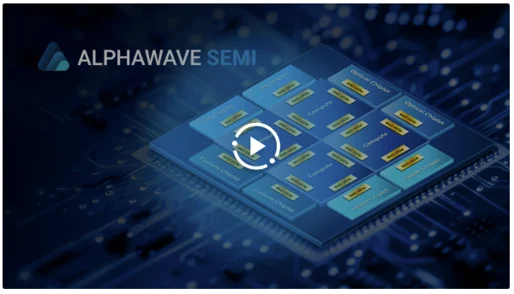

Watch:

How Alphawave Semi’s 64G Gen3

UCIe IP Scale AI Compute and

Connectivity

Watch:

UCIe Compliance Validation

from System Simulation to Silicon

– in Partnership with Keysight

Discover: UCIe Die-to-Die IP Solutions

Alphawave Semi's UCIe IP is enabling the future of AI and high-performance computing. Our low-power, low-latency Die-to-Die PHY IP provides high-bandwidth connectivity for the growing multi-vendor chiplet ecosystem. Learn more about our configurable and integrated solutions.

Analysis: Redefining XPU Memory for AI Data Centers

Custom HBM technology paired with die-to-die interfaces provides a powerful solution to address the critical XPU memory bottlenecks faced by AI chips. Learn more about the benefits of custom HBM implementations and how our in-house silicon expertise and connectivity IP solutions can facilitate design deployment.

Additional Resources

If you would like to find out more about Alphawave Semi and how its custom silicon IP can help you, please get in touch, or visit our resources page for a wide range of white papers and information.