SerDes

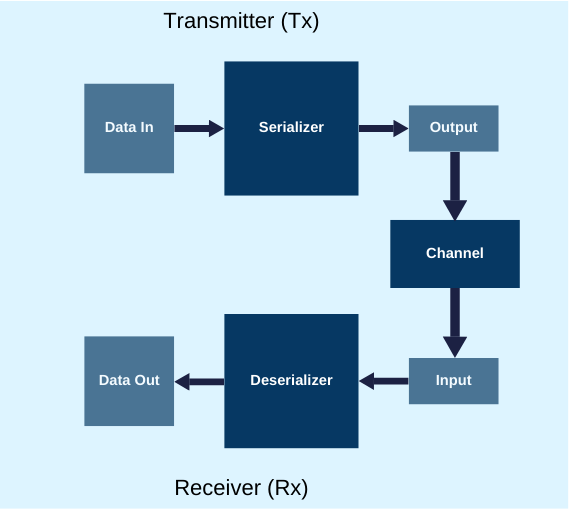

A SerDes is a pair of functional blocks used in high-speed communications to convert data between serial and parallel forms in both directions.

It is principally used to facilitate the transmission of data over a high-speed serial link by reducing the number of I/O pins required and in doing so, minimize the complexity, cost and the potential signal integrity issues associated with parallel data buses.

Serial links can operate at higher frequencies with improved signal integrity over longer distances compared to parallel buses, which suffer from issues like skew, crosstalk, and electromagnetic interference (EMI) at high speeds. Serial data transmission also simplifies routing on PCBs and facilitates higher data throughput with lower power consumption.

As a result, SerDes is essential when transmitting data between chips and systems, for example via PCIe and Ethernet in a data center setting, as well as between chiplets on an SoC.

Fig 1: The use of SerDes (bottom) minimizes the I/O count, complexity, cost and the potential signal integrity issues associated with parallel data buses