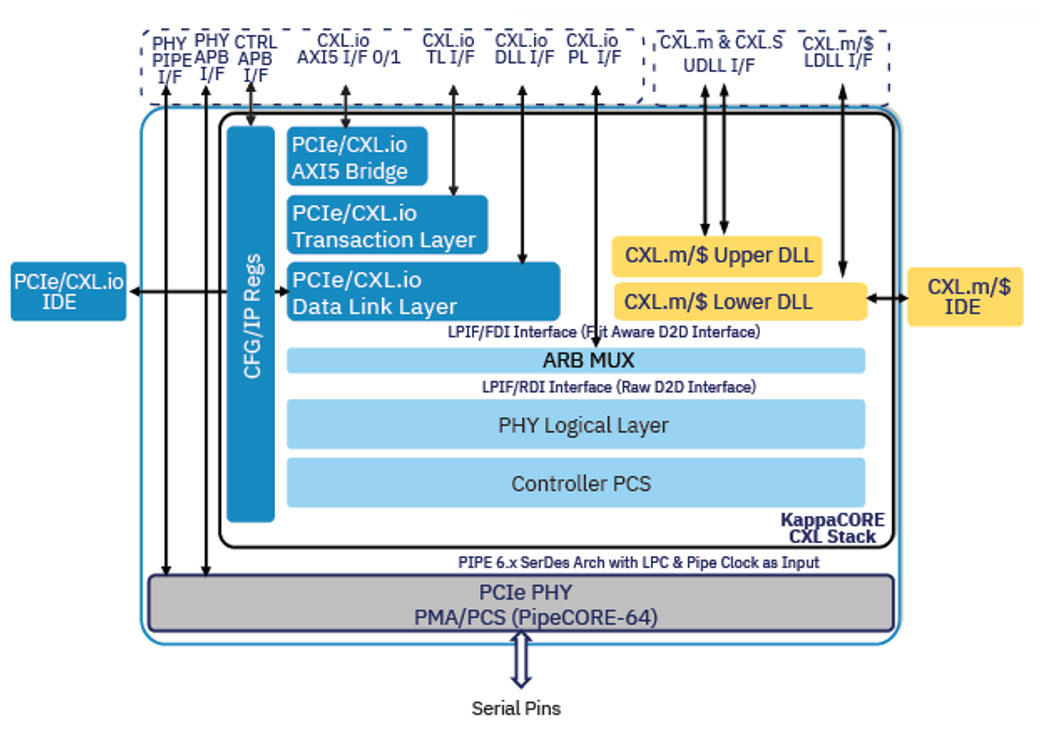

KappaCORE-64 CXL Controller

The KappaCORE-64 from Alphawave Semi is a CXL™ Controller IP that implements the latest CXL 3.0 spec, which is backward compatible with CXL 2.0 and CXL 1.1 specs. This controller forms a complete CXL solution, when integrated with Alphawave Semi’s PipeCORE-64 PCIe PHY IP.