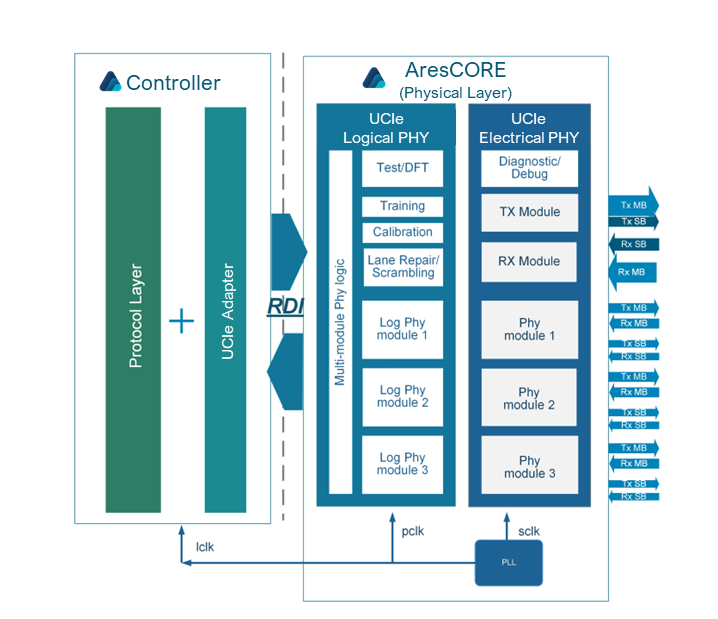

AresCORE UCIe Die-to-Die PHY IP

AresCORE is a market leading extremely low-power, low-latency Universal Chiplet Interconnect Express (UCIe™) Die-to-Die PHY IP designed by Alphawave Semi for very high bandwidth connections between two dies that are on the same package. Its main target applications include, but are not limited to:

- High-Performance Computing (HPC)

- Data Centers

- Artificial Intelligence (AI)

- Networking